# PROCEEDINGS OF THE 9<sup>TH</sup> OVERTURE WORKSHOP

**Electrical and Computer Engineering** Technical Report ECE-TR-2

# DATA SHEET

Title: PROCEEDINGS OF THE 9TH OVERTURE WORKSHOP Subtitle: Electrical and Computer Engineering Series title and no.: Technical report ECE-TR-2

Authors: Sune Wolff & John Fitzgerald Department of Engineering – Electrical and Computer Engineering, Aarhus University

**Internet version**: The report is available in electronic format (pdf) at the Department of Engineering website http://www.eng.au.dk.

Publisher: Aarhus University© URL: http://www.eng.au.dk

Year of publication: 2012 Pages: 125 Editing completed: June 2011

**Abstract**: This report contains the proceedings of The 9th Overture Workshop, held in Limerick on 20th June 2011.

Keywords: Overture, Workshop, 2011

**Please cite as:** Sune Wolff & John Fitzgerald, Proceedings of the 9<sup>th</sup> Overture Workshop 2012. Department of Engineering, Aarhus University. Denmark.125 pp. - Technical report ECE-TR-2

Front image: Logo, Overture Open Source Community

ISSN: 2245-2087

Reproduction permitted provided the source is explicitly acknowledged

# PROCEEDINGS OF THE 9<sup>TH</sup> OVERTURE WORKSHOP

Sune Wolff — Aarhus University, Department of Engineering John Fitzgerald — Newcastle University

Abstract

This report contains the proceedings of the 9th Overture Workshop, held in Limerick on 20th June 2011.

## **Table of Contents**

| Abstract                                                                                                                                | i   |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction                                                                                                                            | 1   |

| List of Participants                                                                                                                    | 3   |

| Run-Time Validation of Timing Constraints for VDM-RT Models                                                                             | 4   |

| Automated Exploration of Alternative System Architectures<br>with VDM-RT                                                                | 17  |

| Facilitating Consistency Check between Specification and Im-<br>plementation with MapReduce Framework                                   | 32  |

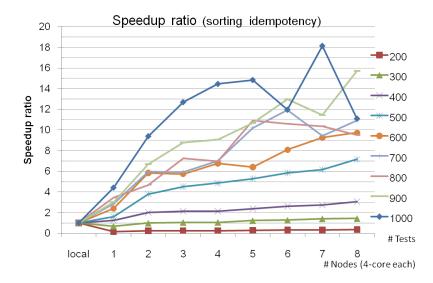

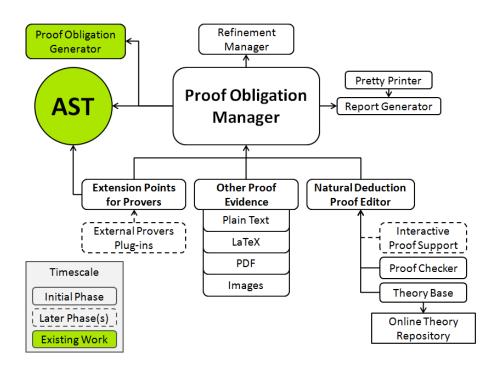

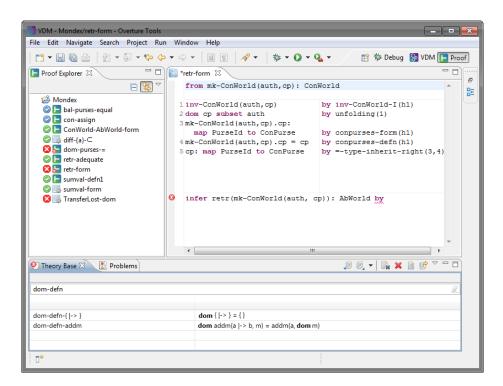

| Counterpoint: Towards a Proof-Support Tool for VDM                                                                                      | 41  |

| VDM++ as a Basis of Scalable Agile Formal Software Devel-<br>opment                                                                     | 50  |

| Towards Customizable and Bi-directionally Traceable Trans-<br>formation between VDM++ and Java                                          | 59  |

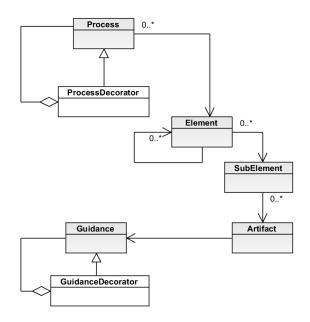

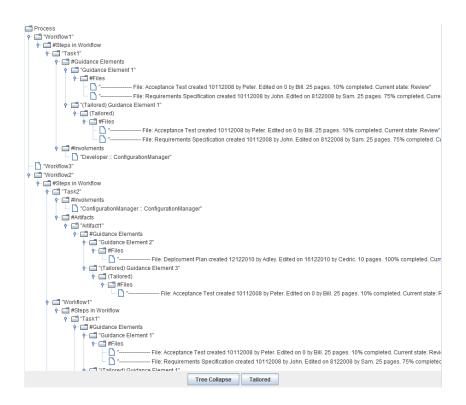

| Utilizing VDM Models in Process Management Tool Develop-<br>ment: an Industrial Case                                                    | 72  |

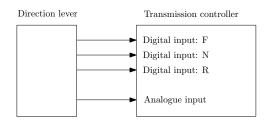

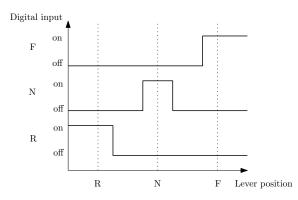

| Formal Modelling and Safety Analysis of an Embedded Control<br>System for Construction Equipment: an Industrial<br>Case Study using VDM | 84  |

| Request for Modification of periodic thread definitions and<br>duration and cycles statements                                           | 120 |

ii

## Introduction

Overture (www.overturetool.org) is by now a well established open-source community initiative that has developed a range of modern tools to support the construction and analysis of models expressed in the VDM (Vienna Development Method) family of notations. Similarly, the community's workshops have become a fixture since the first such event was held in 2005.

This volume represents the proceedings of the ninth Overture Workshop, held at LERO, Limerick, Ireland on 20 June 2011, as part of the FM 2011 symposium. As with all the Overture workshops, its purpose was to foster an active community of researchers and practitioners working with VDM in both academia and industry. The organizers were:

- Sune Wolff of Aarhus University in Denmark, and

- John Fitzgerald of Newcastle University, UK.

Members of the Programme Committee were:

- Nick Battle, UK;

- Dines Bjørner, Denmark;

- Cliff Jones, UK;

- Peter Gorm Larsen, Denmark;

- Ken Pierce, UK;

- Nico Plat, Netherlands; and

- Shin Sahara, Japan.

For the ninth workshop, we were delighted to welcome contributions from Augusto Ribeiro, Kenneth Lausdahl and Peter Gorm Larsen on the real-time extensions VDM-RT, addressing issues that, along with those raised in Ken Pierce's contribution on threads, have been highlighted by the ongoing work on co-modelling and co-simulation for embedded systems design in the DESTECS

1

#### Table of Contents

project (www.destecs.org). Also in the control systems domain was a thorough and systematic analysis of the safety analysis of power transmission in construction equipment by Takayuki Mori from Komatsu in Japan.

Papers by Shigeru Kusakabe, Yoichi Omori and Keijiro Araki, and by Hiroshi Mochio and Fuyuki Ishikawa, provided a more methodological strand to the workshop, while Claus Ballegaard Nielsen's paper on VDM's application in analysing a process management tool provided a further application story.

Ken Pierce's paper on proof construction looked to a long-running area for tools development, coupled closely to deep semantic issues, complemented by a presentation from Anne Haxthausen (not in these proceedings), on the Semantics of a VDM Core Language in COQ.

The papers and presentations are available on-line on the Overture project web-site (http://www.overturetool.org), which also includes online proceedings of the previous Overture workshops. We hope that this volume shows the continuing variety of research and application in the community surrounding this formal method.

October 2011

Sune Wolff John Fitzgerald

2

## List of Participants

Nick Battle Fujitsu UK John Fitzgerald Newcastle University Anne Haxthausen Technical University of Denmark Fuyuki Ishikawa National Institute of Informatics Shigeru Kusakabe Kyushu University Peter Gorm Larsen Aarhus School of Engineering Kenneth Lausdahl Aarhus School of Engineering Hiroshi Mochio Chikushi Jogakuen University Takayuki Mori Newcastle University Claus Nielsen Aarhus School of Engineering Nico Plat West Consulting B.V. Ken Pierce Newcastle University Augusto Ribeiro Aarhus School of Engineering Shin Sahara CSK Corporation Marcel Verhoef CHESS Embedded Technology B.V. Sune Wolff Aarhus School of Engineering Jim Woodcock University of York

3

### Run-Time Validation of Timing Constraints for VDM-RT Models

Augusto Ribeiro, Kenneth Lausdahl, and Peter Gorm Larsen

Aarhus School of Engineering, Dalgas Avenue 2, DK-8000 Aarhus C, Denmark, {ari, kel,pgl}@iha.dk

**Abstract.** Development of distributed real-time embedded systems is often a challenging task and validation of the timing behaviour of such systems is typically as important as its functional correctness. VDM-RT is a modelling language with an executable subset that can be used to describe distributed real-time embedded systems. In previous work [5], post-analysis of important timing constraints was achieved by inspecting a log file that results from simulating a VDM-RT model using VDMTools. In this paper we present how validation of such timing constraints actually can be efficiently carried out during run-time using the interpreter from the open source Overture/VDM tool suite.

**Keywords:** VDM-RT; real-time distributed embedded systems; timing properties validation

#### 1 Introduction

Development of distributed real-time embedded systems is often a challenging task. Typically, real-time embedded systems have timing constrains that should be respected for the system to be considered useful. These timing constrains are obvious for a hard real-time system where the failure to respond within a certain time interval can lead to total system failure but even soft real-time systems can have time constrains. For example, when a user presses the TV remote control to change channel, he expects the channel on the TV to change in an acceptable amount of time.

Using modelling tools to gain better understanding of a system is seen as a good practice [3]. By using simulation, one can gain confidence that a model is doing what it is expected. By being able to define time constrains and validate these constrains in a model during simulation, one could gain even more confidence.

VDM-RT is a modelling language that permits the specification of distributed realtime systems which has an executable subset. In this article, we present a tool enhancement for the VDM-RT interpreter [10] that extends the work presented in [5] and adds the capability of defining timing constrains to a model and validate them during interpretation.

This paper starts off with a short presentation of the relevant aspects in Section 2. Afterwards Section 3 introduces a small case study for an in-car navigation and radio system and illustrates how the existing tools can be used to provide a graphical overview of the interpretation of such an example distributed over multiple CPUs. Then Section 4 introduces the notion of system-wide timing invariants suggested by this article. This is followed by Section 5 illustrating how such timing invariants can be used concretely in VDM-RT and how the tool support can be updated with visualisation of violation of such timing invariants. Finally Section 6 provides a few concluding remarks about the work presented in this article.

#### 2 VDM-RT

The Vienna Development Method (VDM) [2, 8, 6] was originally developed at the IBM laboratories in Vienna in the 1970s and as such it is one of the longest established formal methods. VDM comes in three different flavours: VDM-SL [12] (VDM Specification Language) an ISO Standard; VDM++ [7] an object oriented extension of VDM-SL that supports concurrency; and more recently VDM-RT [14, 13], an extension to VDM++ to model distributed real-time embedded systems. VDM-RT is supported by Overture Tool [9] and VDMTools [4]. Both tools includes an interpreter capable of running the executable part of VDM-RT but the work described in this article is only built into Overture.

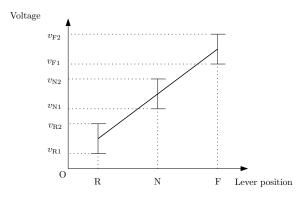

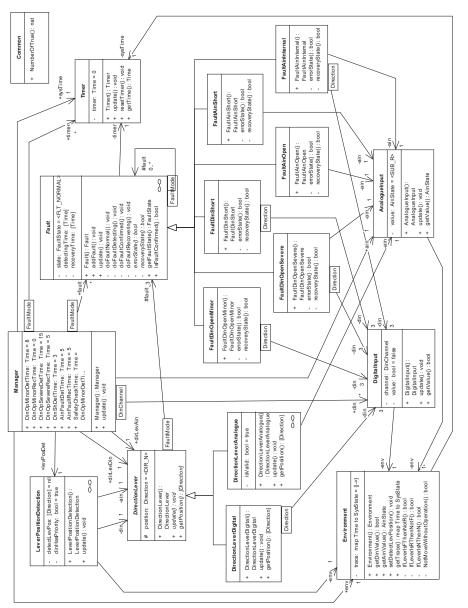

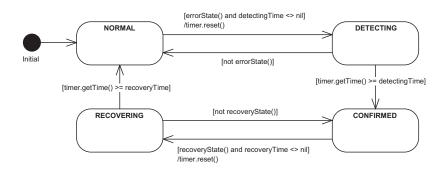

VDM-RT includes the notion of a quantifiable time; there is a system clock which is running from beginning till the end of interpretation. Currently, the maximum precession allowed in the interpreter is 1 nanosecond. It also contains the notion of processing units; the built-in CPU class can be used to declare processing unit and its speed (in Hz); different parts of the model are deployed to specified CPUs. CPUs can communicate between themselves through buses. VDM-RT constructs take time to be interpreted, this time is shorter or longer according to the CPU speed. Using the keywords cycles and duration it is possible to influence how much time a construct takes to execute. Using cycles one can say how many CPU cycles an instruction will take to complete; using this keyword will make the speed to complete an instruction inversely proportional to the speed of the CPU. On the other hand, the keyword **duration** turns the completion time of an instruction to a constant value; this can be useful to model, for example, a IO access where it takes a constant time independent of the speed of the CPU accessing it. There is also a special kind of CPU, which is present in all the VDM-RT models implicitly, the virtual CPU (vCPU) which per default is infinitely fast and its execution does not affect system timing. When a VDM-RT model is interpreted, a log is produced in which all events related with operations and function calls, object and threads creation, activation and deactivation that happened during the interpretation are registered. This log can be visualized graphically like shown in Figure 2.

A special kind of predicates called permission predicates, can act as a guard to operations and can be used to ensure synchronization of concurrent threads. Within these predicates it is possible to use operation history guards. History guards denote the number of requests, activations and completions of the operations. For each of these possible operation states, an event is generated in the log. The VDM-RT syntax to express these events is **#req** for request, **#act** for activate and **#fin** for finish. The *request* event indicates that the interpreter wishes to call the operation. The *activate* event indicates that the requested method was actually activated, this distinction is made because there might exist a delay between request and activation either due to a synchronization condition in the operation or because the CPU executing the thread might not have enough processing power. The *finish* event indicates that the operation has completed. The relative timing of these events are important in case timing requirements for the system being modelled are needed.

#### 3 Case study

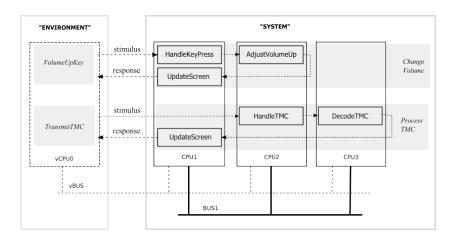

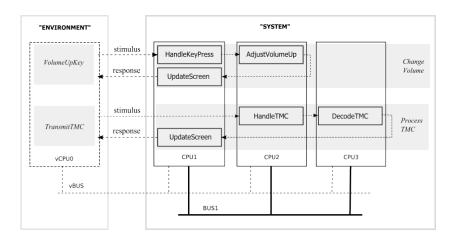

In this section, we introduce a VDM-RT model and the associated existing tool support. The idea behind the model is to describe an in-car navigation radio and check if it is possible to validate its timing requirements. An overview of the system is presented in Figure 1. The environment has three types of interaction with the system, it is possible

Fig. 1. Overview of the In-car Radio Navigation System

for the system to receive new TMC broadcasts (Traffic Message Channel) and adjust the volume (the volume down interaction is not presented in Figure 1 because it is similar to adjusting the volume up). The system is divided into three major components, the man-machine interface (MMI) in CPU1, the radio in CPU2 and the navigation system in CPU3. All these CPUs are connected through a common bus (BUS1). Finally all the CPUs have a connection through the vBUS to the vCPU where the environment is present. Listing 1.1 shows how the Radio class is modelled in VDM-RT.

```

class Radio

values

public MAX : nat = 10;

instance variables

public volume : nat := 0;

```

```

operations

async public AdjustVolumeUp : () ==> ()

AdjustVolumeUp () ==

( cycles (1E6) skip;

if volume < MAX

then ( volume := volume + 1;

RadNavSys 'mmi.UpdateScreen(1)));

async public HandleTMC: () ==> ()

HandleTMC () ==

( cycles (1E6) skip;

RadNavSys 'navigation.DecodeTMC());

end Radio

```

Listing 1.1. Snippet of the Radio class

It has 3 operations (AdjustVolumeDown is not presented), the ones to adjust volume and one that handles the incoming TMC signal. The operations illustrate the use of the keyword cycles, in this case it means that  $10^6$  cycles (1E6) are used in the computation of the operation. The rest is on purpose kept very simple, the AdjustVolume operations change the volume if they did not reach the limit and notifies the screen to do an update. The HandleTMC, relays the decoding of the TMC signal to the navigation unit.

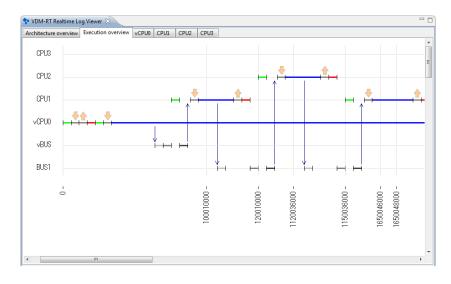

Currently, the tool support available is capable of producing a detailed log of the execution of a VDM-RT model. There is also a tool, the RTLogViewer that allows graphical visualization of such logs. Figure 2 shows RTLogViewer at work. The log

Fig. 2. Log showing one of the executions of the model

contains details such as when certain parts of the model were active and which calls were made at a certain time. Note that the time unit used on the log is nanoseconds (*ns*) as opposed to the time unit used throughout the rest of this article which is milliseconds (*ms*).

A number of system-wide timing invariants need to be added to the in-car navigation system in order to provide a good user interface experience.

- **C1:** A volume change must be reflected in the display within 35 ms.

- C2: The screen should be updated no more than once every 500 ms.

- **C3:** If the volume is to be adjusted upwards and it is not currently at the maximum, the audible change should occur within 100 ms.

It can be argued that C1 and C2 are clashing since we demand the screen to update within 35ms after a key press (in C1) and that the screen only updates each 500ms (in C2) but this was chosen on purpose for testing reasons.

#### **4** Timing Invariants

*Timing invariants* are logical statements that allow a modeller to formulate systemwide timing properties, these properties indicate a relation between two events. These properties have the form of a predicate over events and operate in a three value logic (true, false and unknown). Because these properties are to be verified in a VDM-RT environment we can use in their definition the notion of time. Informally, a property consists of a 6-tuple containing at least the following<sup>1</sup>:

- **A name:** the property name (P);

- A relation: a relation between the two events and a time interval  $(\Box)$ ;

- A trigger: an event that triggers the validation of a conjecture  $(e_t)$ ;

- An ending: when the ending event happens, the conjecture can be checked for satisfiability  $(e_e)$ ;

- A time interval: the time interval used in the property (i);

- A default evaluation: the default evaluation (*true* or *false*) to be returned if the ending event never occurs (*d*).

We attempt to formally define a property P. To assist us in this task we need the function *time* (t) that returns an event time of occurrence.

$$t(e) = \begin{cases} \text{time} & \text{if } e \text{ occured} \\ \varnothing & \text{if } e \text{ did not occur} \end{cases}$$

Where *time* is the systems time of the occurrence of event e. If both events (trigger and ending) occurred then  $t(e_e) \ge t(e_t)$ . The current system time is denoted by *curr*. As expected, it is only possible to evaluate if a property holds if the trigger event  $e_t$  occurs but it might be possible to evaluate it before the ending event  $e_e$  occurs or even if it does not occur at all.

$<sup>^{-1}</sup>$  We say at least because extended versions of the property will appear.

$$P(\sqsubset, e_e, e_t, i, d) \equiv \begin{cases} t(e_e) - t(e_t) \sqsubset i & \text{if } t(e_e) \neq \emptyset \land t(e_t) \neq \emptyset \\ d & \text{if } t(e_e) = \emptyset \land \text{curr} - t(e_t) > i \end{cases}$$

(1)

Where the kind of the property in question determines which relation is ( $\Box$ ) and the default evaluation (d). Because simulation is time framed, it can happen that it terminates before a property can be properly evaluated (the case where  $t(e_e) = \emptyset \land \text{curr} - t(e_t) \le i$ ), when this happens the property evaluation is deemed *inconclusive*.

Now that we have the generic property formally defined, we can by specifying P,  $\Box$  and *d* in definition 1 derive at least three interesting properties.

1. **Deadline Met:** A deadline by definition is a time by which something must be finished. In real-time embedded systems there is typically deadlines that must be respected from when an event happens to its response. In our terminology, it means that the ending event must happen within a certain timeframe from the trigger event. We instantiate 2 and fixate P, □ and *d* for the *deadlineMet* property in the following way:

$$deadline(\leq, e_1, e_2, i, false) \tag{2}$$

Just for better comprehension, the expanded version of definition 2 is presented below:

$$\text{deadline}(e_1, e_2, i) \equiv \begin{cases} t(e_e) - t(e_t) \le i & \text{if } t(e_e) \ne \emptyset \land t(e_t) \ne \emptyset\\ \text{false} & \text{if } t(e_e) = \emptyset \land \text{curr} - t(e_t) > i \end{cases}$$

(3)

2. **Separate:** Intuitively, separation properties describe a minimum separation between events if the second event occur at all and it can be defined through specifying 1 in the following way:

$$separate(>, e_1, e_2, i, true)$$

(4)

3. **Separate Required:** Intuitively, required separations are separations in which the second event is required to occur after the minimum separation. Again we define it by specifying 1:

$$separateReq(>, e_1, e_2, i, false)$$

(5)

There is only a subtle difference between definitions 4 and 5. The default evaluation ensures the desired result when evaluating the separation properties.

A peculiar case happens when the ending event does not occur while interpreting a model. Since a model is simulated within a time range  $(t_n)$ , the ending event could potentially happen some time in the future after the simulation has stopped. In this case, the property would evaluate to *inconclusive* if  $t_n - t(e_t) \leq i$  or to the default evaluation (false) otherwise. This case requires attention by the modeller because it is not possible to tell if the ending event would happen in the future and change the evaluation of the property.

#### 4.1 Events

The basic concept of properties have been described and it was mentioned that properties are predicates over events but no definition of event has been provided yet. In this section we will provide a formalization of the notion of events as used in the timing invariants. Events are defined as predicates over certain occurrences that happen in the model during the interpretation. Events can be divided into two types:

**Operation events:** the VDM-RT semantics defines three identifiable states of an operation: *request*, when an operation is registered to be invoked; *activation*, when an operation is really invoked (the time of *request* and *activation* can be different for several reasons); and finally *finished*, when an operation call is completed.

An *operation event* is an event tied to one of these operation states either at class or object level<sup>2</sup>. So basically when an event is associated with an operation state and a class, this event is registered whenever any object of this class invoking the operation enters that state. On the other hand, an event associated with an object is only registered when the specific object enters that state. Assuming that *opStateSet* is a set that contains tuples of the form (*object*, *op*, *state*) which is populated with the operations that are in a certain state in an object for the current system time (*curr*). We formalize the object level event as:

$$objOpEvent(object, op, state) \equiv (object, op, state) \in opStateSet$$

(6)

The class level event can be formalized with the help of definition 6 as:

$$classOpEvent(class, op, state) \equiv \\ \exists (obj, op, state) \in (opStateSet).obj \in class \land objOpEvent(obj, op, state)$$

(7)

**Predicate events:** this kind of events is associated with a predicate, the event occurs when the predicate is true. These predicates must have as argument at least one instance variable that is accessible from the system class, i.e. any variable that is accessible after initialization of the system. Assuming a predicate p with n arguments we formalize predicate events as:

$$predEvent(p, a_1, \dots, a_n) \equiv p(a_1, \dots, a_n)$$

(8)

At least one instance variable has to be used as argument because predicate events are only evaluated in case of a variable state change. The reason for this is that evaluated all predicate events at all times could be computationally expensive. By tying a predicate with a variable state change, the number of times the predicate is evaluated is possibly highly reduced.

Timing invariants contain two events, a trigger and an ending, as shown in Section 4. Each trigger and ending event can be formed by a combination of operation and predicate event. Here follows the definition of a timing invariant event (trigger or ending):

$$timInvEvent(opEv, predEv) \equiv \begin{cases} opEv & \text{if predEv is not defined} \\ predEv & \text{if opEv is not defined} \\ opEv \land predEv & \text{otherwise} \end{cases}$$

(9)

<sup>&</sup>lt;sup>2</sup> For practical reasons we limit the object level to instance variables present in the system class

If both events are defined, the opEv takes precedence over the *predEv* since it only makes sense to calculate the later if the first one evaluates to true.

#### 4.2 Invariant Instances

A timing invariant typically needs to be validated more than once for each simulation, for each time the trigger event occurs. These are denominated *invariant instances* because they are instances of the same invariant triggered in different situations. The lifetime of a single instance of an invariant is described below:

- 1. Before the trigger event occurs, the instance does not exist;

- 2. If at a certain point in time, the trigger event happens, an instance of the invariant is created in which the time of the trigger event is registered. We denominate these instances *active*;

- 3. If the ending event occurs, the time of its occurrence will be registered in all<sup>3</sup> the instances of the invariant. The instances are marked as ended and its evaluation can be made. We denominate these instances *decommissioned*. This decommissioning policy is called *non-selective*;

- 4. If an instance does not hold it remains saved for later display.

Invariant instances represent fully specified versions of the timing invariants presented in definition 1 where all the free variables have been fixed. An arbitrary number of instances of an invariant can exist at a certain point in time during simulation.

Assuming *timInv* is the set of defined timing invariants, *actInst* is the set of active instances, *decoInst* the set of decommissioned instances we can define the transition of states at a given time. Definition 10 describes how invariant instances are created from invariant definitions. The function *isTrigger* checks if the trigger event of an invariant is occurring. The function *createInst* creates an invariant instance from a definition and registers it in the current time.

$$\forall inv \in timInv.isTrigger(timInv) \implies createInst(timInv) \cup actInst$$

(10)

Definition 11 describes how an instance passes from active to the decommissioned state. Function *isEnding* is analogous to *isTrigger* but for the ending event.

$$\forall inv \in timInv, inst \in \text{instances}(inv, actInv).\text{isEnding}(timInv) \implies \text{actInst} \setminus inst \wedge (\neg \text{isSatisfied}(inst) \implies inst \cup \text{decoInst})$$

(11)

The function *isSatisfied* checks if an instance of the invariant holds or not. By following this strategy, in the end of an interpretation we will end up with the invariant instances that did not hold in the set *decoInst*.

The *matching* policy The *non-selective* decommissioning policy of invariant instances might not be the proper solution for all cases. With this policy it is not possible to describe that an ending event can only decommission one instance. Assuming that  $e_t$

<sup>&</sup>lt;sup>3</sup> Further in this section another way of decommissioning the instances is described.

and  $e_e$  are trigger and ending events respectively, for a certain invariant P. Considering the following string of events:

$$e_t, e_t, e_e \tag{12}$$

With the policy described before, the following would happen: two instances of the invariant P would be created, one for each  $e_t$  then both instances would be decommissioned by the only  $e_e$ . One can think of another policy that instead of keeping a set of active instances, keeps a sequence. In this mode, we demand that the trigger and ending events happen in couples for the invariants to be decommissioned. This kind of decommissioning uses a *matching* policy. By doing this, if the string of events presented in definition 12 ocurrs, one instance of the invariant will still be active. Both policies are possible to be implemented and we decided to delegate the policy selection by extending with one more argument to the timing invariant presented in definition 1.

$$P(\Box, e_e, e_t, i, d, m) \tag{13}$$

The boolean argument m means *match* and decides if the decommissioning of instances is made according to the *matching* policy.

**Other policies** In Section 4.1, operation events over classes were discussed. Defining a class operation event can lead to the situation where an invariant is triggered by one object of that class and ended by another object of the same class. In certain situations this might not be exactly what the modeller is looking for. Hence one more possible policy of decommissioning of instances is a policy that demands that the trigger and the ending event occur on the same object. Another restriction that might appear natural is to demand that the trigger and ending event occur in the same thread. The choice of the policies is model specific or even invariant specific, it depends on what is the modeller looking for in each individual case.

One more possible extension to definition 13 is to add extra fields to enable more policies. The definition extension will not be made here since these are presented here merely for completion and discussion sake. All the mentioned policies in this paper are possible to implement and they have been present in the development phase of the prototype. The final decommissioning policy chosen for the prototype was the *matching* policy simply because it was the most appropriate fit for the example we chose.

#### 5 Run-Time Invariant Checking

A part of what was described in Section 4 was implemented as a prototype as part of this work. The prototype has been built on top of the open-source VDM-RT interpreter VDMJ [1]. As the validation is made during run-time, an option could be added to the interpreter to stop the execution when an invariant is violated. The prototype merely logs the violations which then can be analysed post to simulation completion.

We defined the concrete syntax for the timing invariants in VDM-RT as:

property(trigger,ending,interval);

This syntax is open to discussion and it might need to be extended if the policies need to be expressed in it. The time interval has also some novelty that is noteworthy, it is now possible to specify the time unit used in the interval (s,ms,ns). The concrete syntax of the time interval definition is the following:

interval = **nat1** ("s" | "ms" | "ns")

This notation is used in the examples that appear in the next subsection.

#### 5.1 Concrete Invariants

The invariants first mentioned in Section 3 can now be expressed in the defined syntax.

C1: A volume change must be reflected in the display within 35 ms.

```

deadlineMet(

#fin(Radio`AdjustVolumeUp),

#fin(MMI`UpdateScreen),

35 ms)

```

C2: The screen should be updated no more than once every 500 ms.

```

separate(

#fin(MMI`UpdateScreen),

#fin(MMI`UpdateScreen),

500 ms)

```

**C3:** If the volume is to be adjusted upwards and it is not currently at the maximum, the audible change should occur within 100 ms.

```

deadlineMet(

( #req(MMI`HandleKeyPressUp),

RadNavSys`radio.volume < Radio`MAX

),

#fin(MMI`AdjustVolumeUp),

100 ms)</pre>

```

The definitions are pretty self-explanatory, **#req** and **#fin** refer to the operation states request and finish respectively. The operation events are all defined over classes and one instance variable event is defined in C3. C3 trigger is a composite of a operation and a variable trigger.

#### 5.2 System Class Extension

We recommend an extension to the system where the modeller could specify the system timing properties. We recommend such extension because these properties could be seen as a kind of system-wide timing invariants which must hold in order for the system to behave correctly. The only difference from traditional VDM invariants is that the violation of these would not cause the interpretation to stop but instead report a timing invariant violation which could after be inspected by the modeller.

```

system Sys

...

timing invariants

deadlineMet(evTrigger1, evEnder1, 400 ms);

...

separate(evTrigger2, evEnder2, 1000 ms);

end Sys

```

With the facilities provided by [11], it is possible to easily test the system in different architectures. By coupling this idea with the recorded time invariants in the system class, it is possible to easily spot which architectures respect the time behavior specification and discard the ones which do not.

#### 5.3 Results

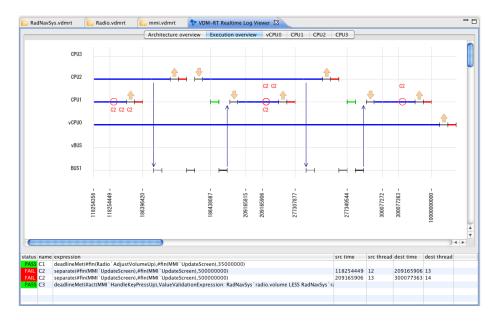

Figure 3 shows the resulting log of an interpretation of the model with the timing invariants. We can see that both C1 and C3 hold through the interpretation while C2 is violated twice. The log shows which invariants were violated or not and for the ones that were violated, it indicates at which point of time it happened and the responsible thread. In the graphical log representation, the places of the violation of C2 are also marked with a circle in red. Having such information readily available and facilities to go to critical points avoids a painstakingly examination of the RTLogs by the modeler, greatly enhancing his ability to reason about the model.

The results of invariants test might not be as simple as only *Pass* or *Not Pass*, like mentioned in Section 4 results might be *Inconclusive* or the invariant might not even be activated once because the trigger event has not occured at all in the chosen scenario, leading to a *Not Activated* result.

#### 6 Concluding Remarks

In this paper we have presented an extension of the VDM-RT notation and the associated interpreter to make validation of system timing properties during run-time that builds up on the theory presented in [5]. The intention of this paper is to both demonstrate that such validation is possible to do at run-time and also to form basis for discussion on the inclusion of timing invariants in the VDM-RT language as a form of

Fig. 3. Timing invariants violations represented in the logger

recording system-wide invariants related with timing which are usually very important when specifying a real-time system. The discussion could also be extended to which kind of the properties should be available for specifying these timing invariants or if their semantics needs to be adjusted. Finally we hope that the workshop can clarify whether it would be worthwhile for the user to be able to select whether violations of timing constraints should be logged or treated as run-time errors.

#### Acknowledgements

This work was partly supported by the EU FP7 DESTECS Project. We appreciate the input we have had from the different partners on this work. In addition we would like to thank Nick Battle and the anonymous referees for valuable input on this paper.

#### References

- 1. Battle, N.: VDMJ User Guide. Tech. rep., Fujitsu Services Ltd., UK (2009)

- Bjørner, D.: The Vienna Development Method: Software Abstraction and Program Synthesis, Lecture Notes in Computer Science, vol. 75: Math. Studies of Information Processing. Springer-Verlag (1979)

- Fitzgerald, J.S., Larsen, P.G.: Balancing Insight and Effort: the Industrial Uptake of Formal Methods. In: Jones, C.B., Liu, Z., Woodcock, J. (eds.) Formal Methods and Hybrid Real-Time Systems, Essays in Honour of Dines Bjørner and Chaochen Zhou on the Occasion of Their 70th Birthdays. pp. 237–254. Springer, Lecture Notes in Computer Science, Volume 4700 (September 2007), iSBN 978-3-540-75220-2

- Fitzgerald, J.S., Larsen, P.G.: Triumphs and Challenges for the Industrial Application of Model-Oriented Formal Methods. In: Margaria, T., Philippou, A., Steffen, B. (eds.) Proc. 2nd Intl. Symp. on Leveraging Applications of Formal Methods, Verification and Validation (ISoLA 2007) (2007), also Technical Report CS-TR-999, School of Computing Science, Newcastle University

- Fitzgerald, J.S., Larsen, P.G., Tjell, S., Verhoef, M.: Validation Support for Real-Time Embedded Systems in VDM++. In: Cukic, B., Dong, J. (eds.) Proc. HASE 2007: 10th IEEE High Assurance Systems Engineering Symposium. pp. 331–340. IEEE (November 2007)

- Fitzgerald, J.S., Larsen, P.G., Verhoef, M.: Vienna Development Method. Wiley Encyclopedia of Computer Science and Engineering (2008), edited by Benjamin Wah, John Wiley & Sons, Inc

- 7. Fitzgerald, J., Larsen, P.G., Mukherjee, P., Plat, N., Verhoef, M.: Validated Designs for Object-oriented Systems. Springer, New York (2005), http://www.vdmbook.com

- Jones, C.B.: Systematic Software Development Using VDM. Prentice-Hall International, Englewood Cliffs, New Jersey, second edn. (1990), iSBN 0-13-880733-7

- Larsen, P.G., Battle, N., Ferreira, M., Fitzgerald, J., Lausdahl, K., Verhoef, M.: The Overture Initiative – Integrating Tools for VDM. ACM Software Engineering Notes 35(1) (January 2010)

- 10. Lausdahl, K., Larsen, P.G., Battle, N.: A Deterministic Interpreter Simulating a Distributed Real Time System using VDM. Submitted for publication (2011)

- 11. Lausdahl, K., Ribeiro, A.: Automated Exploration of Alternative System Architectures with VDM-RT. In: 9th Overture Workshop, June 2011, Limerick, Ireland (2011)

- P. G. Larsen and B. S. Hansen and H. Brunn N. Plat and H. Toetenel and D. J. Andrews and J. Dawes and G. Parkin and others: Information technology – Programming languages, their environments and system software interfaces – Vienna Development Method – Specification Language – Part 1: Base language (December 1996)

- Verhoef, M.: Modeling and Validating Distributed Embedded Real-Time Control Systems. Ph.D. thesis, Radboud University Nijmegen (2008), ISBN 978-90-9023705-3

- Verhoef, M., Larsen, P.G., Hooman, J.: Modeling and Validating Distributed Embedded Real-Time Systems with VDM++. In: Misra, J., Nipkow, T., Sekerinski, E. (eds.) FM 2006: Formal Methods. pp. 147–162. Lecture Notes in Computer Science 4085 (2006)

### Automated Exploration of Alternative System Architectures with VDM-RT

Kenneth Lausdahl and Augusto Ribeiro

Aarhus School of Engineering, Dalgas Avenue 2, DK-8000 Aarhus C, Denmark

**Abstract.** Choosing the optimal deployment of a distributed embedded application onto alternative hardware configurations is often difficult and time consuming. When developing a new product, a company must chose a hardware architecture that ensures both that the system behaves correctly according to its functional and timing specifications but also keeps its production cost at a minimum. The investigation to find this tradeoff between cost and performance can be very expensive if carried out at implementation time. A company can save money and development time if there is a possibility to quickly explore the design alternatives before the start of the implementation. In this paper we describe a method and associated tool support to assist in finding the best system design solution.

#### 1 Introduction

As distributed real-time embedded systems become more and more prevalent around us, new techniques must to be used to ensure lower costs of development while keeping the service quality high. The quality of these kind of systems is normally not only measured by functional correctness but also by timing behaviour correctness. Because timing correctness is so essential when developing such systems, the implementation cost can increase considerably if it is discovered at later stages of the development that the selected hardware architecture cannot fulfil the timing parameters. Typical design questions that cross an architect's mind are [13]:

- 1. Does the proposed architecture meet the performance requirements of all applications?

- 2. How robust is the chosen architecture with respect to changes in the application or architecture parameters?

- 3. Is it possible to replace components by cheaper, less powerful equivalents to save cost while maintaining the required performance targets?

Models of software/hardware can be used to assist the system architect in answering these questions. They have previously been used to explore and validate different deployment architectures even before the implementation cycle starts [14,12]. By doing so, it is possible to gain knowledge, at an early stage, of the product that is being developed, even before any deployment decisions have been made. Usually, companies that wish to develop a distributed embedded system have certain target Printed Circuit Boards (PCBs) in mind, which support a small limited range of CPUs. These PCBs establish the architecture of the hardware and by using models and simulation techniques, one can gain insight into which PCB should be selected in order to fulfil the project requirements. Furthermore, one can identify which kinds of CPUs and buses are needed to respect the speed/capacity requirements of the application. Having a method and tool support to test out all the interesting PCB/CPU/bus combinations and identify which ones satisfy the system timing invariants, would give the system architect an advantage when making such initial design choices.

The modelling language VDM-RT, enables a system architect to do these kinds of different simulations, but the process of changing the system architecture and application deployment is very cumbersome and lacks both flexibility and tool support. Everything concerning deployment is tightly connected and mixed with the application construction in the *system*<sup>1</sup> class. This makes it difficult and impractical to explore different architectures from a modeller's point of view. When one wants to make such changes, one must either overwrite the **system** class, and by doing so losing the previous system, or create a new project and copy all the files, except the system class, and then create a new system class.

In this paper we show how deployment of VDM-RT models can be modified to support exploration of different hardware configurations without changing the model and how this can help a system architect to find the good designs. This can be seen as a part of a larger effort in order to explore the different design alternatives of an embedded distributed system in the style used in the DESTECS project [2]. We consider "the best design" to be any solution that solves the proposed problem. It is then up to the architect to decide which is the best one based on system invariants and additional cost analysis.

The remainder of this paper is set out as follows. In section 2 an introduction to VDM and the VDM-RT dialect is presented. Section 3 illustrates how we separate the model from its deployment without loosing expressiveness. In section 4, the typical design questions are addressed and solutions are presented to show how this work assists the answering of these questions. Section 5 illustrates how this work can be used to explore an in-car-navigation system. Lastly, section 6 concludes this work with remarks and suggestions for future improvements.

#### 2 The VDM Real-Time Dialect

The Vienna Development Method (VDM) [1,8,4] was originally developed at the IBM laboratories in Vienna in the 1970s and as such it is one of the longest established formal methods. The VDM Specification Language is a language with a formally defined syntax, static and dynamic semantics. Models in VDM are based on data type definitions built from simple abstract types such as **bool**, **nat** and **char** and type constructors that allow user-defined product and union types and collection types such as (finite) sets, sequences and mappings. Type membership may be restricted by predicate invariants. Persistent state is defined by means of typed variables, again restricted by invariants. Operations that may modify the state can be defined implicitly, using pre- and post-condition predicates, or explicitly, using imperative statements. Such operations denote relations between inputs and pre-states and outputs and post-states, allowing for non-

<sup>&</sup>lt;sup>1</sup> The **system** class describes the system architecture and its deployment.

determinism. Functions are defined in a similar way to operations, but may not refer to state variables.

Three different dialects exists for VDM: The ISO standard VDM Specification Language (VDM-SL) [5], the object oriented extension VDM++ [6] and a further extension of that called VDM Real Time (VDM-RT) [15,7]. All three dialects are supported by the open source tool called Overture [9].

VDM++ and VDM-RT allow concurrent *threads* to be defined. In VDM-RT, the concurrency modelling can be enhanced by deploying objects on different CPUs with buses connecting them. Operations called between CPUs can be asynchronous, so that the caller does not wait for the call to complete.

VDM-RT has a special **system** class where the modeller can specify the hardware architecture, including the CPUs and their bus communication topology; the dialect provides two predefined classes for the purpose, CPU and BUS. CPUs are instantiated with a clock speed (Hz) and a *scheduling policy*, either *First-come*, *first-served* (*FCFS*) or *Fixed priority* (*FP*). Only one **system** is allowed to be declared at a time for a single model.

The initial objects (artifacts) defined in the model can then be deployed to the declared CPUs using the CPU's deploy operations. Buses are defined with a transmission speed (bytes/s) and a set of CPUs which they connect. Object instances that are not deployed to a specific CPU (and not created by an object that is deployed), are automatically deployed onto a *virtual CPU*. The virtual CPU is connected to all real CPUs through a *virtual bus*. Virtual components are used to simulate the external environment for the model of the system being developed.

In figure 1 a graphical representation of an in-car navigation radio system is shown, which illustrates deployment with three CPUs connected by a single bus.

Fig. 1. Overview of the In-car Radio Navigation System

The in-car-navigation system shown in figure 1 is represented as a **system** class in listing 1.1. Firstly, the application artifacts are declared as instance variables (mmi,

radio and navigation). The definition of the hardware appears after: in this case three CPUs are declared (CPU1, CPU2 and CPU3) with a bus (BUS1) which connects them. Finally, the system architecture and deployment of the artifacts to the specific CPUs appear in the last section.

```

system RadNavSys

instance variables

-- create artifacts

static public mmi : MMI := new MMI();

static public radio := new Radio();

static public navigation := new Navigation();

-- create CPUs (policy, capacity)

CPU1 : CPU := new CPU (<FP>, 22E6);

CPU2 : CPU := new CPU (<FP>, 11E6);

CPU3 : CPU := new CPU (<FP>, 113E6);

-- create bus (policy, capacity, topology)

BUS1 : BUS := new BUS (<FCFS>, 72E3, {CPU1, CPU2, CPU3})

operations

public RadNavSys: () ==> RadNavSys

RadNavSys () ==

( navigation.setMmi(mmi);

radio.setMmi(mmi);

radio.setNavigation(navigation);

mmi.setRadio(radio);

CPU1.deploy(mmi, "MMI");

CPU2.deploy(radio, "Radio");

CPU3.deploy(navigation, "Nav");

. . .

);

end RadNavSys

```

Listing 1.1. A typical system class

Special system invariants based on timing constraints can be validated through post analysis of log files [3]. This enables the modeller to express time constraints on operations and instance variables; e.g. when volumeUp is called then no later than three time units later the volume must be incremented. Log files used for post analysis can be directly created by the VDM interpreter [10] enabling automated checking of such time constraints, allowing a systematic rejection of models which do not meet the time constraints either because the models are wrongly specified or the architecture used is not powerful enough. At the this point in time only post analysis is possible but a version to check system invariants at run-time is being investigated [11].

#### **3** Ensuring Separation Between Software And Hardware

To enable automated exploration of hardware architectures for VDM-RT models, changes must be made to the way deployment is expressed. Currently, the modeller must create new projects with a custom **system** class for each architecture to be explored. This method is inefficient and difficult to automate. The basic problem with the current system definition is the close coupling between system architecture and system deployment. Ensuring a clear separation between architecture and deployment allows a system to be configured and tested against any number of hardware architectures without the hassle of creating new test projects or changing the system architecture.

This section will present a different approach to express deployment from the current VDM-RT **system** class explained in section 2 while preserving the same run-time properties.

This section will present a different approach to express deployment from the current VDM-RT **system** class shown in section 2 while preserving the same run-time properties. Instead of a single **system** class defining the deployment, our approach uses a four level structure to define deployment, keeping a clear separation between the model and the actual deployment. This allows tool automated exploration at all levels:

Abstract Software Architecture: Defines artifacts and how they depend on each other; Abstract Hardware Architecture: Defines the abstract hardware architecture in terms of nodes and communication channels, i.e. without speeds/capacities or policies;

**Configuration:** Defines deployment of artifacts presented in Abstract Software Architecture to nodes from the hardware present in the Abstract Hardware Architecture;

**Deployment:** Defines a concrete deployment using the Configuration; similar to the constructor in the current **system** class.

For each of the levels above, a concrete definition and the relation between them will be presented as VDM-SL types and functions in the following sections.

#### 3.1 Abstract Software Architecture

The Abstract Software Architecture (ASA) is used to describe which application artifacts exist in the system and where inter-artifact calls occur. It represents the software system at its most abstract point where only artifacts of applications are referred e.g. mmi, radio and navigation from section 2. The ASA contains dependencies between the different artifacts representing the inter-artifact calls in the system. This dependency description is used both (1) to check that a hardware architecture contains the required communication channels and (2) for automatic exploration of hardware architectures fitting the software model. Listing 1.2 shows the VDM types used to represent the ASA of a system.

types

Artifact : seq of char

ASA ::

Listing 1.2. Abstract Software Architecture types.

The Artifact type denotes a named system instance variables (e.g. mmi); the artifacts set denotes the set of artifacts which can be deployed; the dependencies map denotes the dependencies between the artifacts.

#### 3.2 Abstract Hardware Architecture

From an abstract point of view, a computing system is no more than a set of processing nodes which communicate via channels. We name this representation: Abstract Hardware Architecture (AHA). Listing 1.3 presents VDM types capable of representing an abstract hardware architecture.

```

types

Node ::

id : nat1;

ComChannel ::

nodes : set of Node;

AHA ::

nodes : set of Node

channels : set of ComChannels

inv forall c in set channels & c.nodes subset of nodes;

```

Listing 1.3. Abstract Hardware Architecture as a VDM type

A processing node is represented by Node which has an identifier and a communication channel is represented by ComChannel, which contains the set of nodes it connects. AHA defines a hardware architecture containing several nodes and channels connecting them. AHAs can either be automatically generated based on the maximum number of artifacts in the system or manually specified which is often the desired solution for an industry where existing PCBs are available from previous projects.

#### 3.3 Configuration

A configuration describes how a system is deployed to an abstract architecture. This allows a system to be deployed onto a hardware configuration without explicitly spec-

ifying the limitations of the hardware like CPU speed and bus capacity. A configuration defines a relation between artifacts from an ASA and the computing nodes from an AHA. The dependencies stated by an ASA must be reflected in the communication channels of the AHA for the configuration to be valid. This check is done by the function checkDependencies. Listing 1.4 defines a configuration of an ASA to an AHA. A configuration can be created either by automatic permutation of artifacts onto the nodes of an AHA or by manually specifying the relations. The latter is the normal case for an industry where specialized nodes such as processors with integrated GPS<sup>2</sup> modules are used, which will require a GPS artifact to be explicitly deployed to a specific node.

```

types

NodeArtifactRelation : map Node to set of Artifact;

Configuration ::

asa : ASA

aha : AHA

relation : NodeArtifactRelation

inv mk_Configuration(asa,aha,relation) ==

checkDependencies(asa, aha, relation);

```

Listing 1.4. Deployment Configuration

#### 3.4 Deployment

The deployment of a system is the process of restricting the computational power of the nodes and the communication channels. A node must be limited to the computational power of a specific CPU with a maximum number of instructions it can perform per second. The same applies to buses where the transfer rate is limited. Listing 1.5 shows the Deployment type which represents a mapping between Nodes and ComChannels to concrete CPUs and buses.

Listing 1.5. Specifies the type of each computational node and communication channel

<sup>&</sup>lt;sup>2</sup> Global Positioning System

Computational nodes and communication channels are abstractions of the actual physical implementation where a circuit board is manufactured, which among other things consists of the main components CPUs and buses which VDM-RT can reason about. In listing 1.6 two VDM types are listed. CPU represents a computational Node where the node is limited from being infinitely fast to a specific frequency slowing down the execution of instructions. The same applies to the BUS, which is a limited version of the ComChannel, where a transmission speed limits the number of bytes which can be transmitted per second.

```

CPU ::

id

: nat1

speed

: nat1

brand

: seq of char

: <FP> | <FCFS>;

scheduling

BUS ::

: nat1

id

: nat1

speed

: <FILO>;

type

```

Listing 1.6. Hardware types

#### 3.5 New Deployment Work-flow

To use the four layered separation described above some changes must be made to the deployment work flow. However, not all of the above levels require the modeller's direct attention, since most of the changes are conceptual separations of system elements. It is important to understand that the output of the separation proposed above can be mapped to the current VDM-RT system class without losing details. The difference is that this clear separation between the different levels, enables the modeller to do exploration at all levels. It also enables tools to be developed to assist this process.

#### The work-flow in ordinary VDM-RT can be described with the following steps:

- 1. Defining the VDM-RT model.

- 2. Identifying the static artifacts of the model.

- 3. Defining the hardware nodes: CPU and BUS and instantiating the artifacts.

- 4. Deploying the artifacts to the CPUs.

This is currently all done in a single class called **system** with no clear indication of what is artifacts and what is hardware and deployment.

#### The work-flow with the new sub divided structure:

**Model development:** The first step is to develop the actual VDM model as in the current VDM-RT workflow.

- **System configuration:** The modeller configures the artifacts of the system as usual in a VDM-RT system class.

- **Extract artifacts and dependencies:** If all artifact relations are expressed as either artifact constructor arguments or parsed as arguments to operations on artifacts, then this step can be automated. Artifacts will be extracted from the **system** class and their dependencies from the system constructor, enabling an ASA to be created<sup>3</sup>:

- **Composing a new AHA:** The ASA defines the artifacts and their required dependencies while the AHA define an abstract hardware architecture which respects the dependencies from the ASA extracted from the artifacts dependencies. Such an AHA can either be automatically generated based on the ASA or it can be manually specified by the user.

- **Configuration:** The configuration defines how each artifact is linked to a node of the given AHA. This can be specified manually by the user or a range of configurations can be generated from the pair (ASA, AHA).

- **Deployment:** The final deployment is the limitation of an AHA. This can again be specified by the user to a single fixed deployment or the user can enter a set of possible CPUs which could be used per node allowing a range of deployments to be generated to explore these different CPU limitations.

- **Evaluation:** Finally, the model can be executed with a single specific deployment and its system invariants can be checked either through post-analysis or at run-time both leading to an accept / reject verdict of the tested deployment. This indicates to the modeller if this configuration is acceptable to the system leaving the decision of which to choose to the modeller.

The steps described above can be expressed through the formula 1.

$$\left(ASA + AHA\right) \to^* Configuration \to^* Deployment \equiv \texttt{system}$$

(1)

The arrow  $\rightarrow^*$  denotes that many elements can be generated with respect to the left side of the arrow. In the first case one or more *configurations* can exist which configures a particular pair of ASA and AHA. Each configuration defines how the ASA is mapped onto the AHA but does not restrict the hardware in any way. Similar to the *configuration*, one or more *deployments* can exist which restricts a particular *configuration* by limiting each computational node to a specific frequency and each communication channel to a specific speed. Finally it can be seen from the **system** in section 2 that the left side of the formula below is equivalent to the information in the system class in VDM-RT.

#### 4 The Exploration of Alternative System Architectures

Exploring alternative system architectures is supported by VDM-RT and in section 3 it has been described how the process of deployment can be split up into levels which can be explored for alternatives. The goal is to provide the means to answer the questions

<sup>&</sup>lt;sup>3</sup> In this paper we do not deal with references which can be passed between artifacts at run-time which also leads to new dependencies.

stated in the introduction. However because these questions are seen from the modellers point of view, we will try to relate them to the levels of the formula 1 to make it easier to describe how this work provides (partial) answers to these questions.

The requirements extracted from the questions are as follows:

- Exploring alternative artifact distribution on a fixed hardware configuration.

- Exploring alternative hardware configurations for an ASA.

- Exploring alternative deployment parameters for a fixed configuration.

The questions require the exploration to support different distribution of artifacts on a fixed distributed hardware platform; the ability to explore parameters for a specific hardware such as CPU capacity; and finally a way to validate such a system architecture. Futhermore we can add the ability to generate hardware architectures, but this may be mainly of academic value. The requirements stated above are covered in the following subsections. In addition the validation is addressed in section 4.4.

### 4.1 Exploring Alternative Artifact Distribution On A Fixed Hardware Configuration

To explore alternative artifact distribution, an ASA is required to obtain the artifacts and their dependencies. Since the hardware configuration is fixed, an AHA is also provided by the modeller. This gives the pair (ASA, AHA) as input to the exploration of alternative artifact distribution. Formula 2 illustrates where this takes place in the overall work flow where the underlined part denotes what is produced. The result of the generation of alternative distributions is a set of Configurations all for the same system.

$$\left(ASA + AHA\right) \to^* \underline{Configuration} \to^* Deployment \equiv \texttt{system}$$

(2)

Listing 1.7 shows the signature of a VDM function which produces the desired set of configurations:

```

createAltDisbs : ASA * AHA -> set of Configuration

createAltDisbs(asa, aha) == is not yet specified;

```

Listing 1.7. Signature of a function for generation of Configurations from an ASA.

#### 4.2 Exploring Alternative Hardware Configurations For An ASA

When the goal is to find the optimal hardware configuration for a given system it can often be difficult and time consuming to create all possible combinations of nodes and communication channels. It is however important to understand that this is possibly only of academic value since industrial companies often have of-the-shelf hardware platforms which they want to explore. AHAs can be generated from the number of unique artifacts from an ASA. The formula 3 shows where in the overall work flow this exploration contributes again using the underlined part as the produced aspects.

$$\left(ASA + \underline{AHA}\right) \to^* Configuration \to^* Deployment \equiv \texttt{system}$$

(3)

A signature of the VDM function to create the AHAs is shown in listing 1.8. It takes an ASA as input and returns a set of AHAs.

```

createAHAs : ASA -> set of AHA

createAHAs(asa) ==

let maxNodes = card asa.artifacts

in

...

```

Listing 1.8. Signature of a VDM function for the automatic AHA generation.

#### 4.3 Exploring Alternative Deployment Parameters For A Fixed Configuration

Exploring alternative deployment parameters for an otherwise fixed system is one of the most important requirements because this relates directly to the costs of the final product. If a cheaper CPU can be used in mass production, money can be saved by the manufacturer of such a system. Exploring alternative deployment parameters means that one can come up with all possible limitations of the hardware, reducing either a CPUs computational capacity or limiting the bandwidth of a bus. An unlimited range of such deployments can be generated however this is not useful in practice since only a small number of CPUs and buses can be used in a specific hardware topology. In most cases, a PCB design already exists which supports a fixed number of different CPUs from a specific family. Thus the exploration is based on knowing that a small list of possible CPUs or buses are available to be used as nodes. The exploration generates a set of deployments and takes an otherwise fixed system as input together with a set of available CPUs per node of the AHA and a set of available buses for each communication channel. Formula 4 shows where in the overall work flow this takes place.

$$\left(ASA + AHA\right) \to^* Configuration \to^* \underline{Deployment} \equiv \texttt{system}$$

(4)

The signature of a VDM function is shown in listing 1.9 which takes a fixed configuration of a system plus two maps where the available CPUs and BUSs are given for the resources in the AHA.

```

exploreDeployParams : Configuration *

map Node to set of CPU *

```

```

map ComChannel to set of BUS

-> set of Deployment

exploreDeployParams(config, nCm, cBm) == is not yet specified;

```

Listing 1.9. Signature of a VDM function for alternative deployment parameter exploration.

#### 4.4 Evaluation Of The Architectures

The ability to automatically determine if a specific deployment is good enough is very important now that we have presented the functionality to automatically generate alternatives as early as the AHA in the work flow. The potentially results is a very large number of deployments, since a split in the flow at an early stage doubles the output of all later steps. Currently, the only way to determine if a deployment is "good enough" is by manually inspecting the execution log through the graphical viewer named Real-Time Log Viewer. This viewer is able to illustrate how the scheduler creates threads, shifts them in and out in relation to time etc. To overcome the challenge of manual inspection work is being done in [11] to enable run-time checking of system invariants. Such invariants can then express time constraints in the system, which is exactly what is needed when deployments have to be validated. If the modeller provides system invariants expressing the critical time constraints of the model then the run-time checking of these invariants will be able to tell us if a given deployment has not violated any invariants and thus be accepted.

#### 5 Case Study: In-car Radio Navigation

This case study is based on an already known case explored in both [3] and [13]. How this new structure can be used to do deployment exploration will be presented. The new way to express a system configuration is shown in listing 1.10, it can be seen that no deployment is included within the system class. This is very similar to the system from section 2.

```

system RadNavSys

instance variables

-- create artifacts

static public mmi : MMI := new MMI();

static public radio : Radio := new Radio();

static public navigation : Navigation := new Navigation();

operations

public RadNavSys: () ==> RadNavSys

RadNavSys () ==

( navigation.setMmi(mmi);

radio.setMmi(mmi);

radio.setMmi(mmi);

radio.setNavigation(navigation);

mmi.setRadio(radio);

```

```

);

end RadNavSys

```

#### Listing 1.10. In-Car-Navigation system.

A new grammar for deployment in VDM-RT is proposed in listing 1.11, allowing the deployment elements: AHA, configuration and deployment to be specified. All the elements can be generated through exploration as explained in section 4. The listing 1.11 illustrates how the deployment of the in-car-navigation system can be done with this new syntax. The deployment is specified with all elements, but without the ASA, since it can automatically be extracted from the system class in listing 1.10. Any of the blocks **aha**, **configuration** and **deployment** can be left empty in the grammar, indicating that they should be automatically generated. However by explicitly specifying all blocks only a single deployment will exist as in the original system definition from section 2.

#### aha

```

Channel1 := {node1, node2, node3}

configuration

node1 := {mmi};

node2 := {radio}

node3 := {navigation}

deployment

node1 := CPU(200MHz, <FP>)

node2 := CPU(100MHz, <FP>)

node3 := CPU(100MHz, <FP>)

Channel1 := BUS(72E3, <CSMACD>)

```

Listing 1.11. New deployment specification for the In-Car-Navigation system

What if the deployment specified in listing 1.11 is an acceptable deployment but the modeller likes to do future investigation through the third question: *Is it possible to replace components by cheaper, less powerful, equivalents to save cost while maintaining the required performance targets?* One option is to try out deployments where one of the nodes is limited to one of three different CPUs as shown in listing 1.12. It can be seen that the grammar allows nodes to be defined with a set of CPUs instead of a single CPU this allows the exploration to use permutations of CPUs for each node.

#### deployment

```

nodel := {CPU(200MHz, <FP>),

CPU(100MHz, <FP>),

```

```

CPU(50MHz, <FP>)}

node2 := CPU(100MHz, <FP>)

node3 := CPU(1000MHz, <FP>)

Channel1 := BUS(72E3, <FCFS>)

```

Listing 1.12. Alternative deployment block for exploration of deployment parameters.

When the exploration is done for the **deployment** block as shown in listing 1.12, three alternatives will be generated, one with each type of CPU. All these alternatives can then automatically be validated against the same tests to see if all of them fulfils the system invariant<sup>4</sup>. If so the modeller can freely decide which option is the best choice.

#### 6 Concluding Remarks

Choosing the optimal architecture for a system is challenging, not only can it be difficult to determine but VDM-RT currently lacks the ability to allow exploration of alternatives in an efficient way without the need of duplicating the model. This work has proposed a way to enable exploration through separation of model and deployment, where exploration is possible at all levels of the deployment process. The common questions a modeller might ask when choosing a optimal architecture have been addressed and exploration functions proposed. We think that this work will help the system architect to determine an optimal architecture for a given system by enabling easy automated exploration. Such an exploration will be able to create all alternatives of AHA, Configuration and deployments and evaluate them against system invariants. VDM-RT priority settings for functions and operations has not been addressed in this work but will be future investigated in the near future.

The plan is to implement the features described in this paper in the Overture platform such that it can be exploited for automatic co-model analysis in the DESTECS project as well. We expect that this will be completed before the end of 2011.

#### Acknowledgements

This work was partly supported by the EU FP7 DESTECS Project. We appreciate the input we have had from the different partners on this work. In addition we would like to thank Nick Battle for valuable input on this paper.

#### References

- Bjørner, D., Jones, C. (eds.): The Vienna Development Method: The Meta-Language, Lecture Notes in Computer Science, vol. 61. Springer-Verlag (1978)

- Broenink, J.F., Larsen, P.G., Verhoef, M., Kleijn, C., Jovanovic, D., Pierce, K., F., W.: Design support and tooling for dependable embedded control software. In: Proceedings of Serene 2010 International Workshop on Software Engineering for Resilient Systems. ACM (April 2010)

<sup>&</sup>lt;sup>4</sup> The system invariants are not included in this paper but can be found in [3].

- Fitzgerald, J.S., Larsen, P.G., Tjell, S., Verhoef, M.: Validation Support for Real-Time Embedded Systems in VDM++. In: Cukic, B., Dong, J. (eds.) Proc. HASE 2007: 10th IEEE High Assurance Systems Engineering Symposium. pp. 331–340. IEEE (November 2007)

- Fitzgerald, J.S., Larsen, P.G., Verhoef, M.: Vienna Development Method. Wiley Encyclopedia of Computer Science and Engineering (2008), edited by Benjamin Wah, John Wiley & Sons, Inc

- Fitzgerald, J., Larsen, P.G.: Modelling Systems Practical Tools and Techniques in Software Development. Cambridge University Press, The Edinburgh Building, Cambridge CB2 2RU, UK, Second edn. (2009), ISBN 0-521-62348-0

- 6. Fitzgerald, J., Larsen, P.G., Mukherjee, P., Plat, N., Verhoef, M.: Validated Designs for Object-oriented Systems. Springer, New York (2005), http://www.vdmbook.com

- Hooman, J., Verhoef, M.: Formal semantics of a VDM extension for distributed embedded systems. In: Dams, D., Hannemann, U., Steffen, M. (eds.) Concurrency, Compositionality, and Correctness, Essays in Honor of Willem-Paul de Roever. Lecture notes in Computer Science, vol. 5930, pp. 142–161. Springer-Verlag (2010)

- Jones, C.B.: Systematic Software Development Using VDM. Prentice-Hall International, Englewood Cliffs, New Jersey, second edn. (1990), iSBN 0-13-880733-7

- Larsen, P.G., Battle, N., Ferreira, M., Fitzgerald, J., Lausdahl, K., Verhoef, M.: The Overture Initiative – Integrating Tools for VDM. ACM Software Engineering Notes 35(1) (January 2010)

- 10. Lausdahl, K., Larsen, P.G., Battle, N.: A Deterministic Interpreter Simulating a Distributed Real Time System using VDM. Submitted for publication (2011)

- 11. Ribeiro, A., Lausdahl, K., Larsen, P.G.: Run-Time Validation of Timing Constraints for VDM-RT Models. Submitted for publication (2011)

- Verhoef, M.: On the use of VDM++ for Specifying Real-Time Systems. In: Fitzgerald, J.S., Larsen, P.G., Plat, N. (eds.) Towards Next Generation Tools for VDM: Contributions to the First International Overture Workshop, Newcastle, July 2005. pp. 26–43. School of Computing Science, Newcastle University, Technical Report CS-TR-969 (June 2006)

- Verhoef, M.: Modeling and Validating Distributed Embedded Real-Time Control Systems. Ph.D. thesis, Radboud University Nijmegen (2008), ISBN 978-90-9023705-3

- Verhoef, M., Larsen, P.G.: Interpreting Distributed System Architectures Using VDM++ A Case Study. In: Sauser, B., Muller, G. (eds.) 5th Annual Conference on Systems Engineering Research (March 2007), Available at http://www.stevens.edu/engineering/cser/

- Verhoef, M., Larsen, P.G., Hooman, J.: Modeling and Validating Distributed Embedded Real-Time Systems with VDM++. In: Misra, J., Nipkow, T., Sekerinski, E. (eds.) FM 2006: Formal Methods. pp. 147–162. Lecture Notes in Computer Science 4085 (2006)

### Facilitating Consistency Check between Specification and Implementation with MapReduce Framework

Shigeru KUSAKABE, Yoichi OMORI, and Keijiro ARAKI

Grad. School of Information Science and Electrical Engineering, Kyushu University 744, Motooka, Nishi-ku, Fukuoka city, 819-0395, Japan

Abstract. We often need well-formed specifications in order to properly maintain or extend a system by members who were not in charge of the original development. In contrast to our expectation, formal specifications and related documents may not be maintained, or not developed in real projects. We are trying to build a framework to develop specifications from a working implementation. Testability of specifications is important in our framework, and we develop executable, or testable, formal specifications in model-oriented formal specification languages such as VDM-SL. We figure out a formal specification, check it with the corresponding implementation by testing, and modify it if necessary. While the specific level of rigor depends on the aim of the project, millions of tests may be performed in developing highly reliable specifications. In this paper, we discuss our approach to reducing the cost of specification test. We use Hadoop, which is an implementation of the MapReduce framework, so that we can expect the scalability in testing specifications. We can automatically distribute the generation of test cases from a property, the interpretation of the executable specification and the execution of its corresponding implementation code for each test data using Hadoop. While straightforward sequential execution for large data set is expensive, we observed scalability in the performance in our approaches.

#### 1 Introduction

While we are supposed to have adequate documents in ideally disciplined projects, we may not have such documents in many actual projects. In spite of potential effectiveness of formal methods, formal specifications and related documents may not be maintained, or not developed. Nonetheless, we often need well-formed specifications in order to properly maintain or extend a system by members who were not familiar with the details of current implementation.

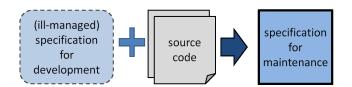

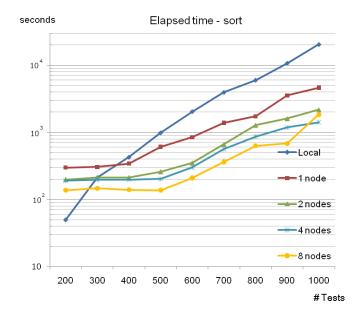

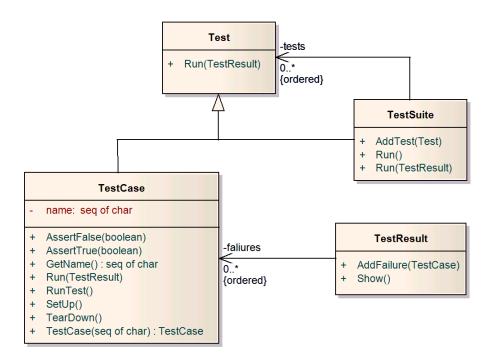

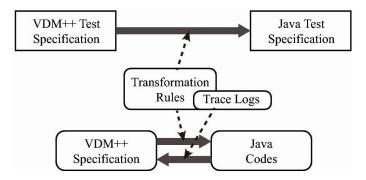

We are trying to build a framework to develop specifications for maintenance from the actual code of working implementation plus ill-maintained specifications for development if they exist. Fig. 1 shows our concept.

We expect we can figure out some specifications by using techniques of software engineering while we assume documents used in the development may be unreliable and members familiar with the detail of the development may be unavailable. However, we will rely on testing to check the consistency between the implementation and the specifications in the process of making the specifications close to ideal ones.

We can develop executable, or testable, formal specifications in model-oriented formal specification languages such as VDM-SL. By using the interpretor of VDMTools,

**Fig. 1.** Developing specifications for maintaining or extending a system from source code plus specifications that are not well managed during the development.

we can test executable specifications in VDM languages to increase our confidence in the specifications. In our framework, we expect executable specifications to play an important role. We develop a formal specification from the running implementation, check it with the result or behavior of the corresponding implementation by testing, and modify and retest it if necessary. In contrast to the usual software development, we modify the specifications to be consistent with the corresponding running code.